Depending on the state of the existing design, this can be seamless, or can be very costly.

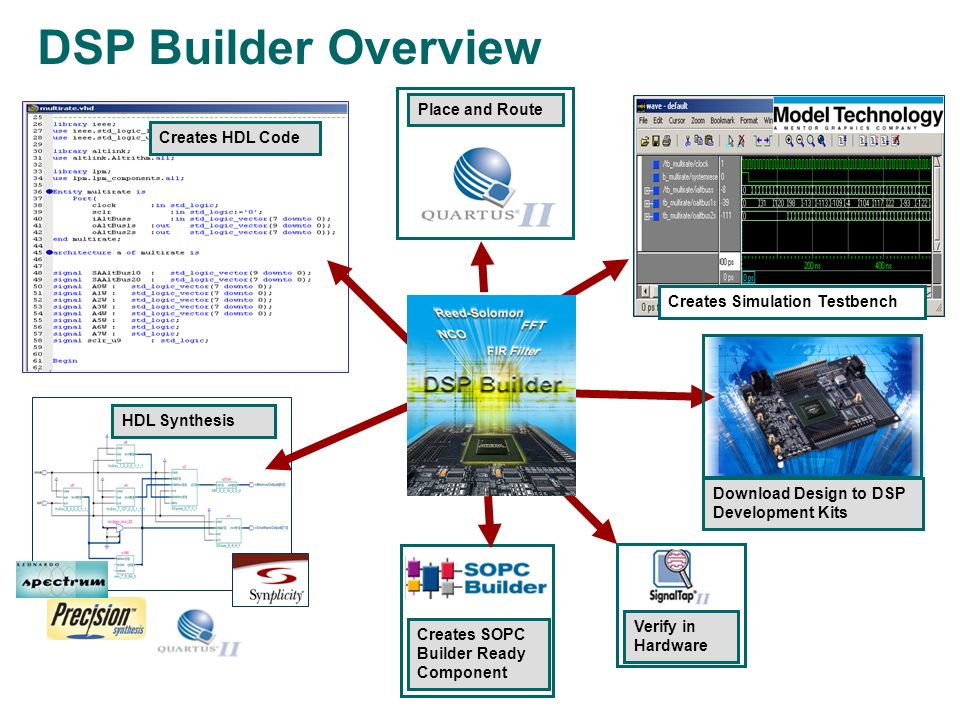

This model will serve as a reference for the new design, and will be used to validate the new design.Ģ) Existing VHDL or Verilog design to be reworked or enhanced. In this case, we very much prefer to work with the customer system engineers to create a Matlab system model (m-code) to use as a baseline for the new design. The most common starting points we see are:ġ) Blank sheet, new system design. Regardless of whether you are reworking an existing design, or starting a new design from scratch, FulcrumDSP is ready. In some cases, the promise of design ease employing higher level design entry tools such as Simulink have just not panned out as well as the sales brochure would indicate.

This is true regardless of whether the engineer is using Xilinx Vivado, or Intel(Altera) Quartus. Today's FPGA solutions have become so complicated that engineers who don't do FPGA design every day are finding the tools too complicated and overwhelming to operate properly.

0 kommentar(er)

0 kommentar(er)